software

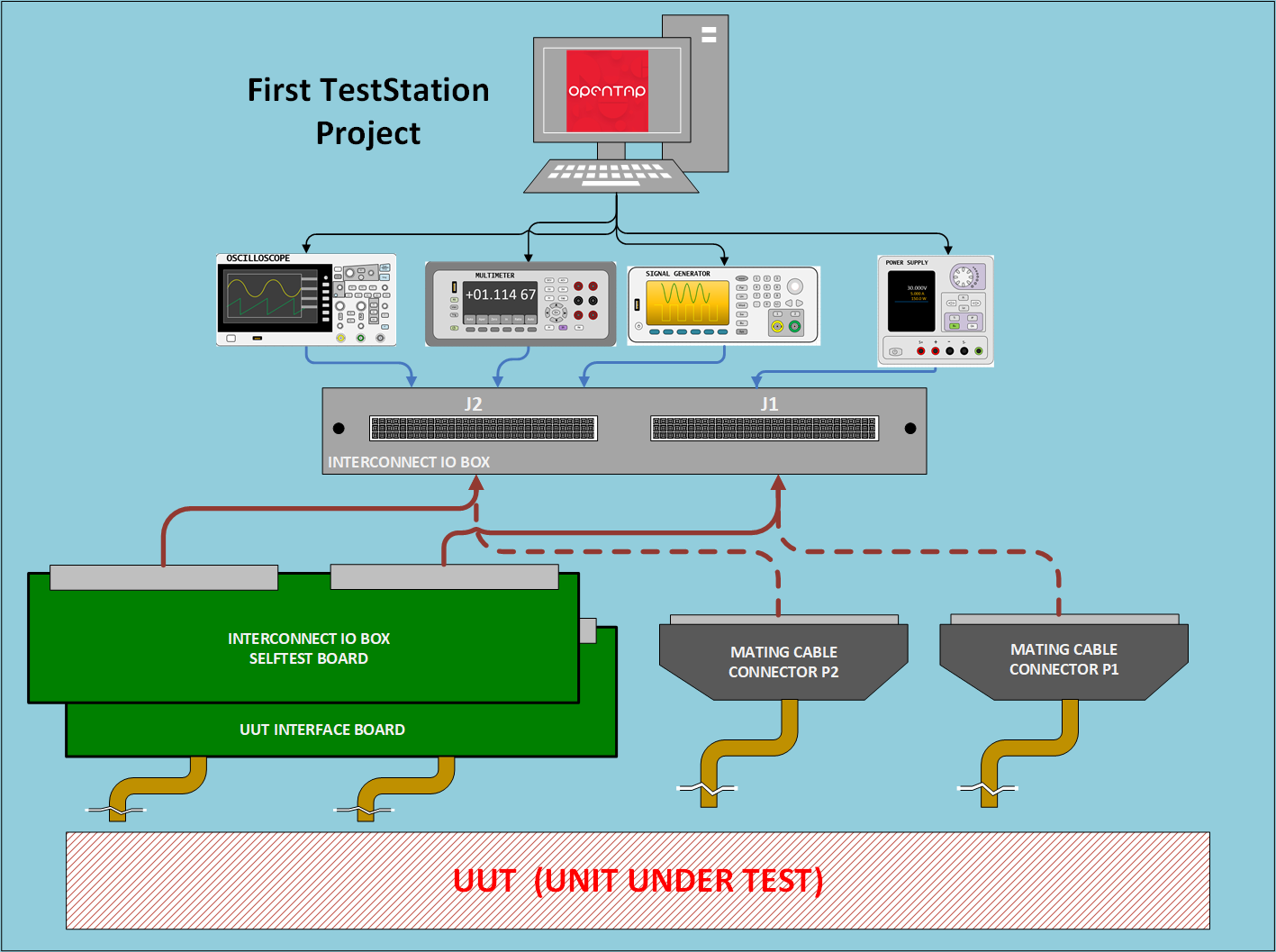

Test Plan Strategy on First TestStation

Features

• On the First TestStation (FTS), the plan was always to design the InterconnectIO Box coupled with the Selftest Board to ensure that the hardware operates as intended and the firmware functions as expected, with minimal bugs.

• The Test Plan for validating the First TestStation was developed following the creation of the Selftest Block Diagram to ensure that the maximum number of hardware components and functionalities are covered in the Test Validation list.

• The Test Validation Plan are part of the InterconnectIO Box in the github repository. For details, refer to the Validation_Test_200-1000.pdf

• The Test Plan sequence has been integrated into the InterconnectIO Box in a built-in format to facilitate the validation and debugging of both the hardware and firmware.

• The design plan is to utilize the OpenTAP environment to transition the built-in Selftest functionality to an external test sequencer.

Flowchart

• The flowchart below illustrates the algorithm used to validate the test procedures of the First TestStation.